存储系统

存储器概述¶

技术指标:

- 存取速度

- 存取时间:完成一次读/写的时间

- 存取周期:连续启动两次访问操作之间的最短时间间隔(略大于存取时间)

- 存储器带宽:单位时间内存储器所能传输的信息量

边界对齐(32 位):

- DW 起始字节地址最末 3 位为 000,地址是 8 的整数倍

- W 起始字节地址最末 2 位为 00,地址是 4 的整数倍

- 半字的起始字节地址最末 1 位为 0,地址是 2 的整数倍

- 单字节不存在边界对齐问题

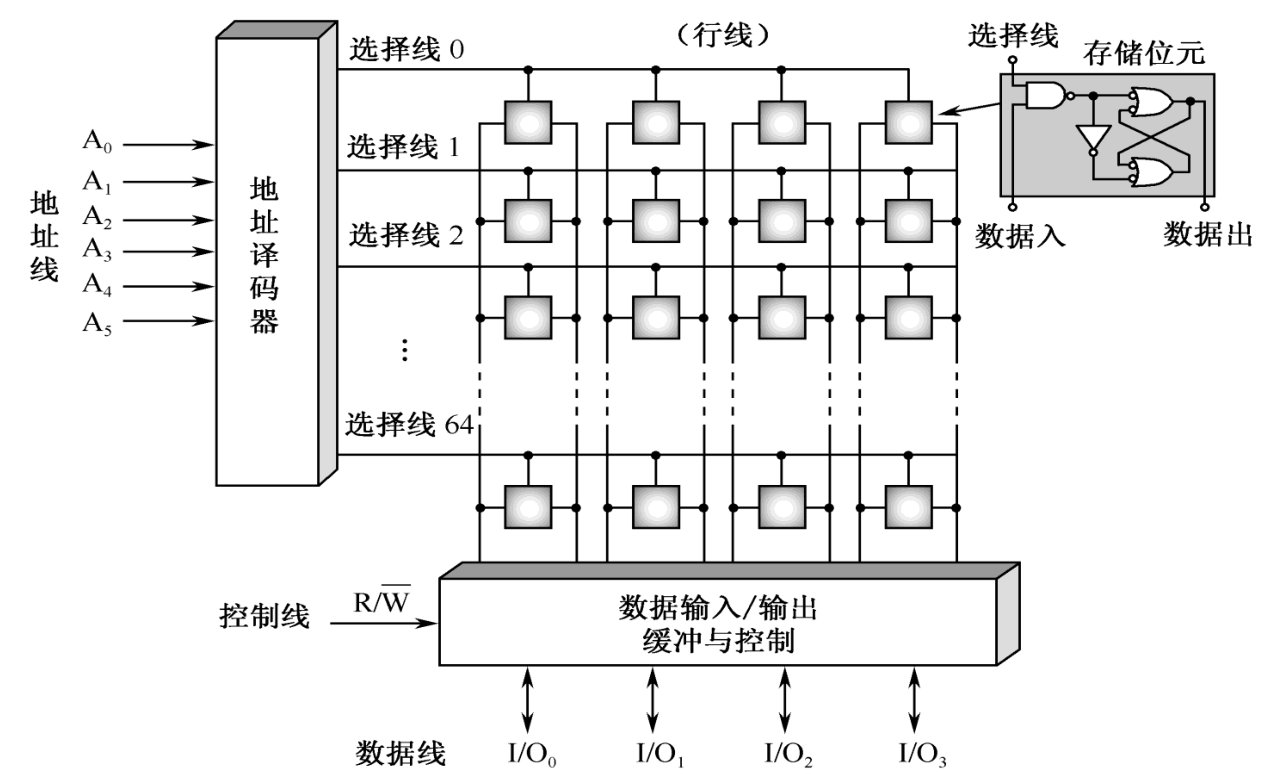

半导体存储器¶

CPU 理论上的最大寻址范围,由 MAR 和 MDR 的大小决定,为 \(2^{\text{MAR}} \times \text{MDR}\).

SRAM¶

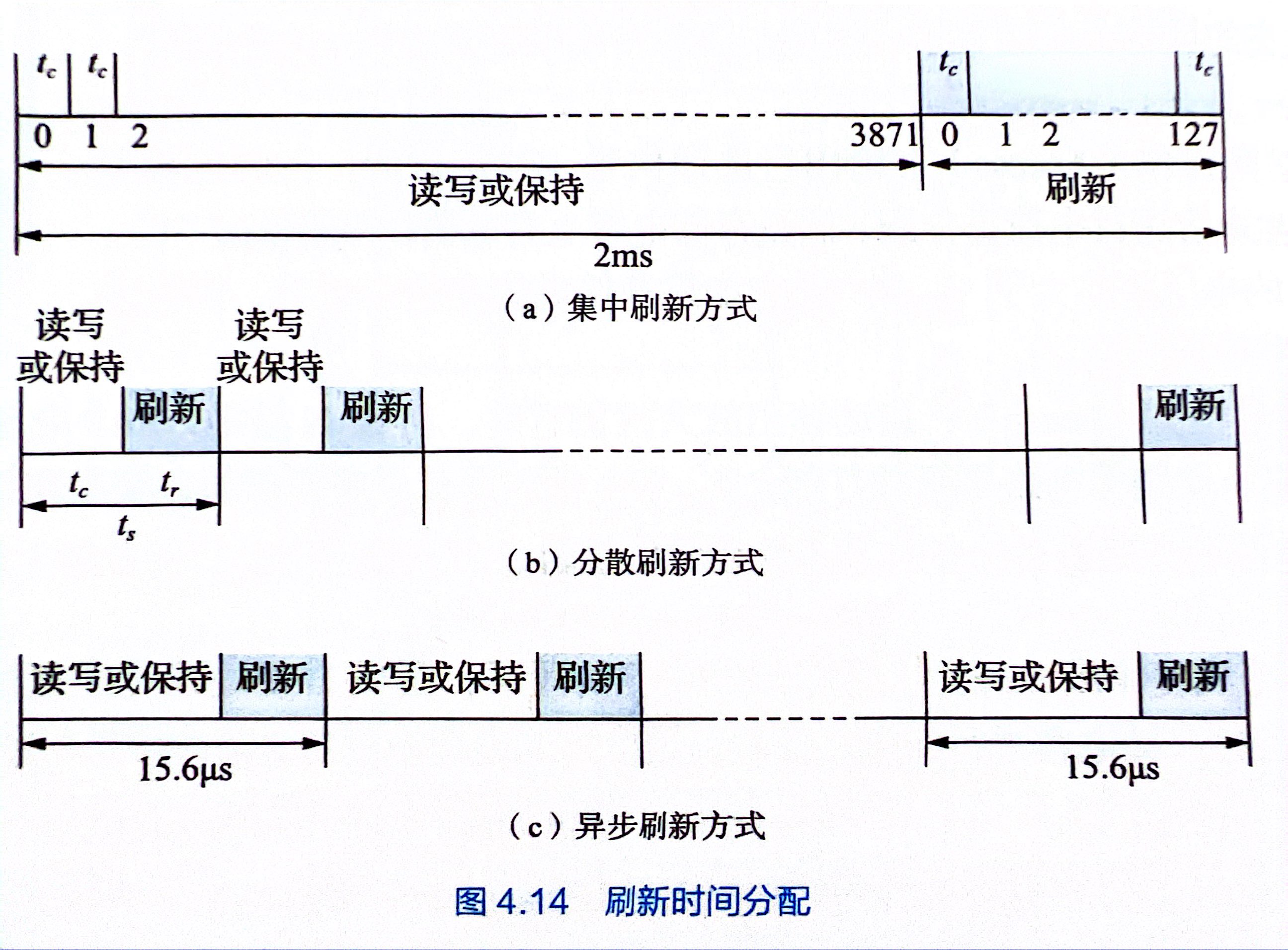

DRAM¶

主存的组织及与 CPU 的连接¶

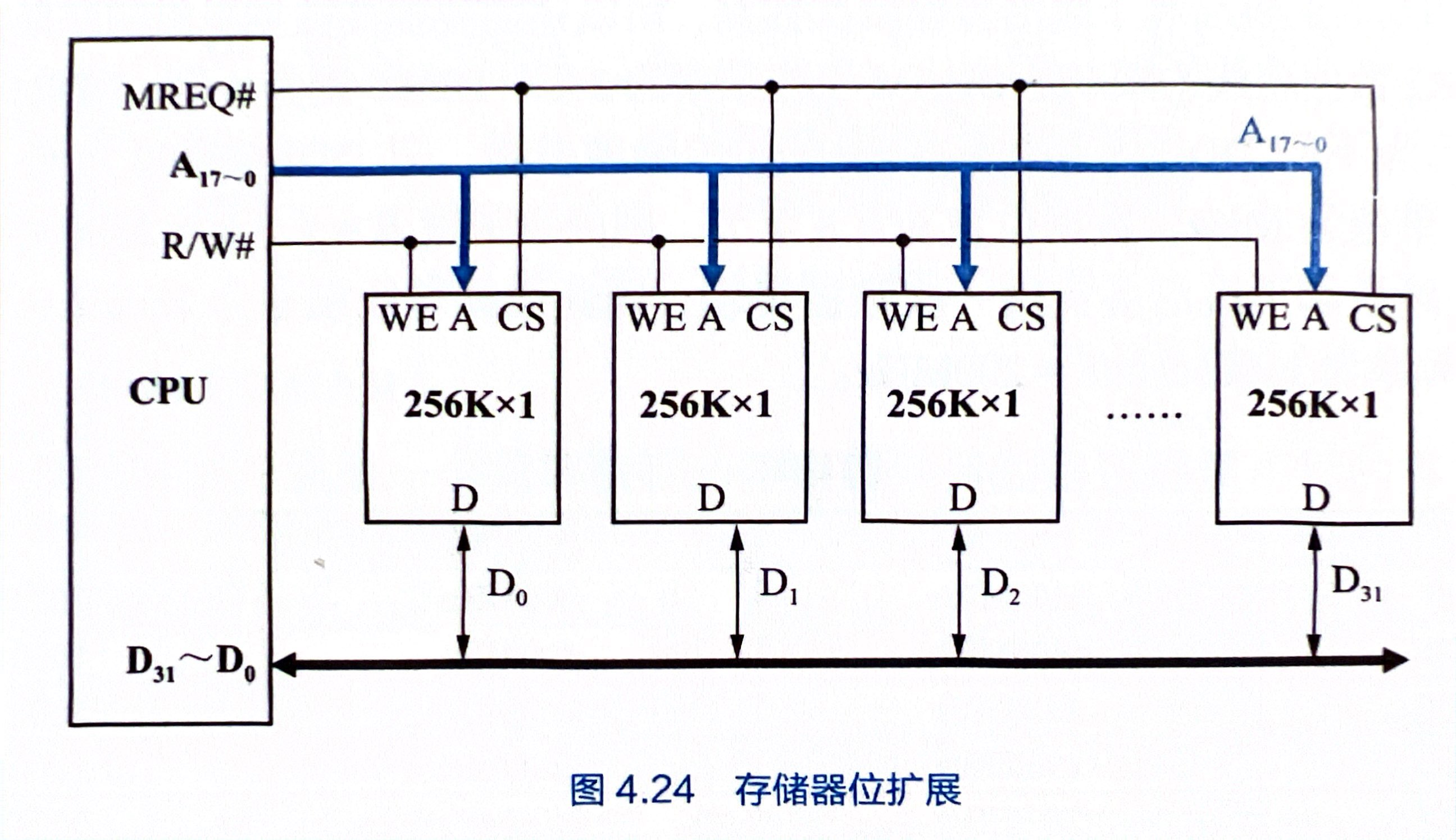

位扩展¶

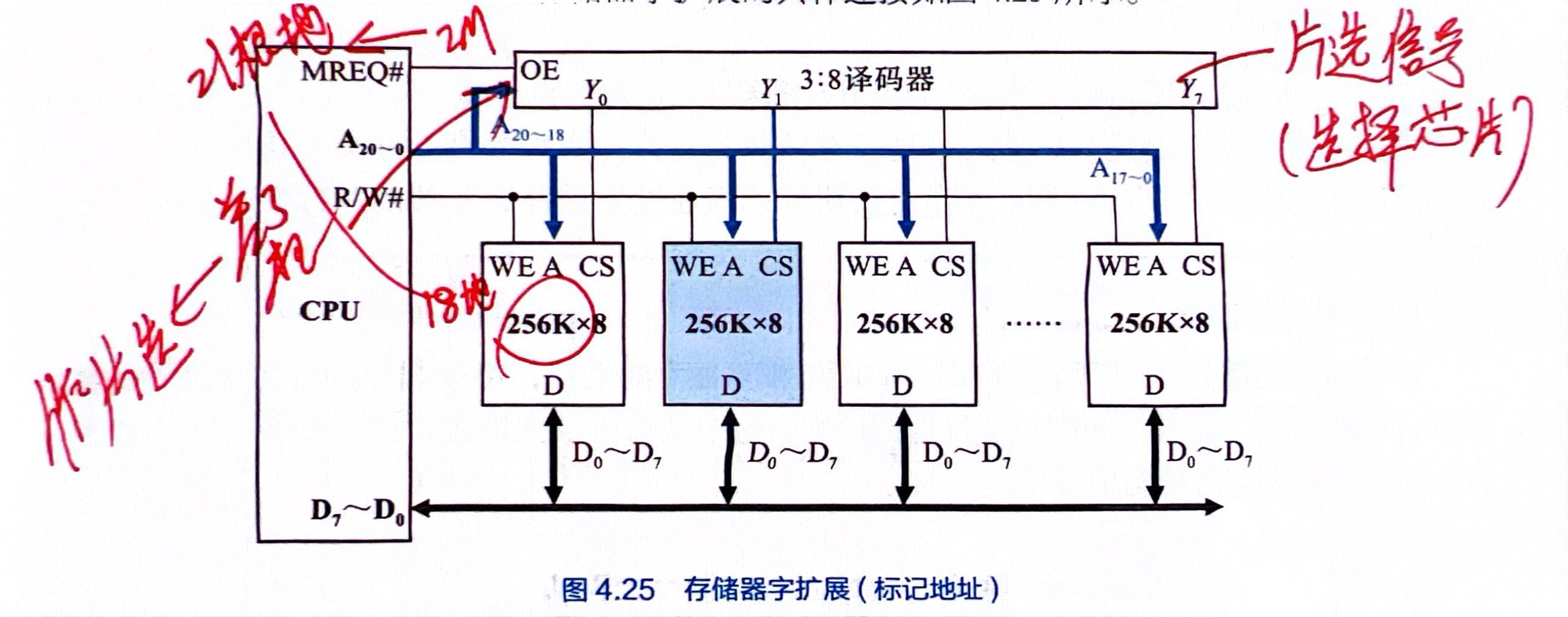

字扩展¶

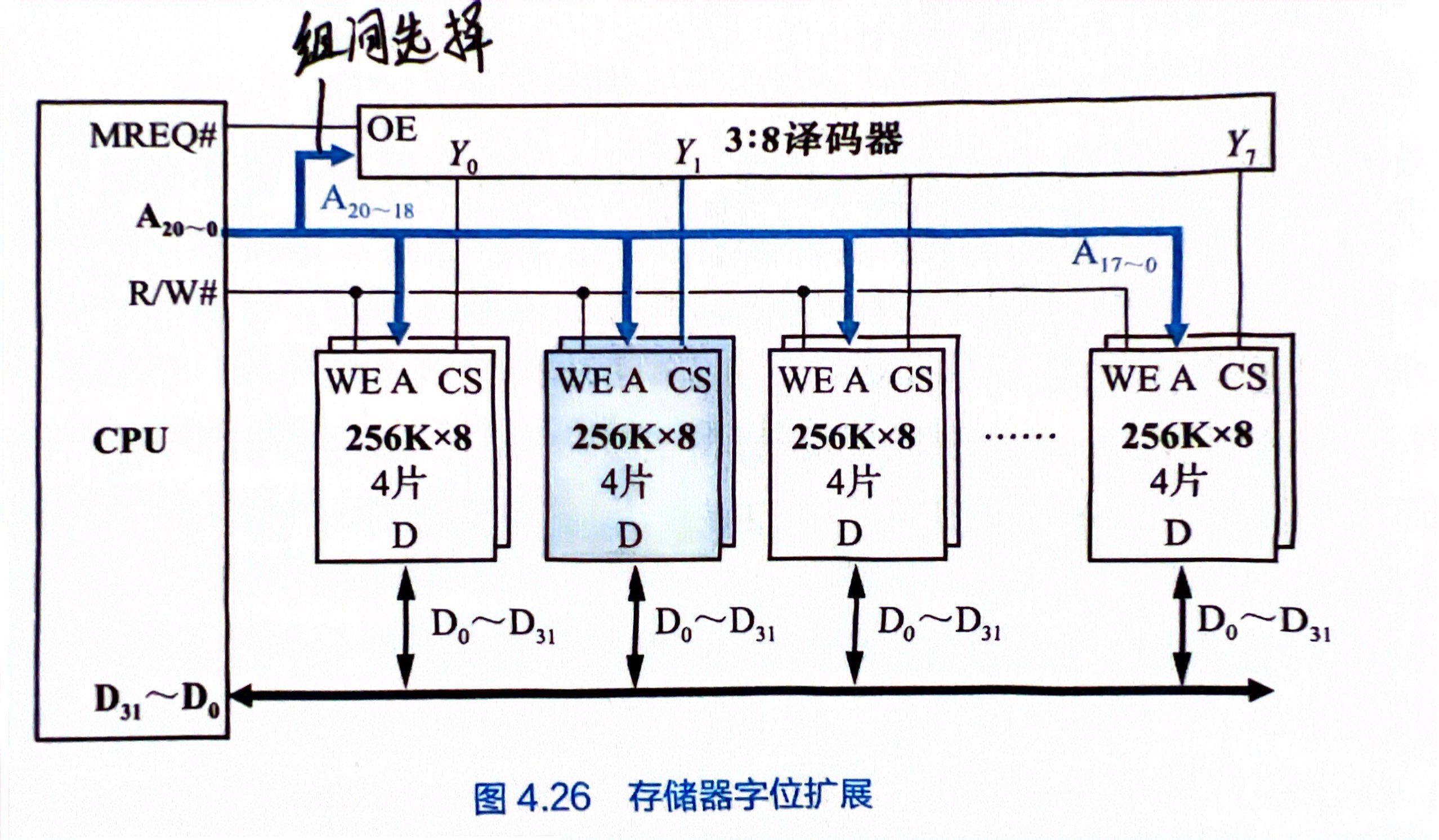

字位同时扩展¶

并行主存系统¶

方法:双端口存储器、单体多字存储器、多体交叉存储器

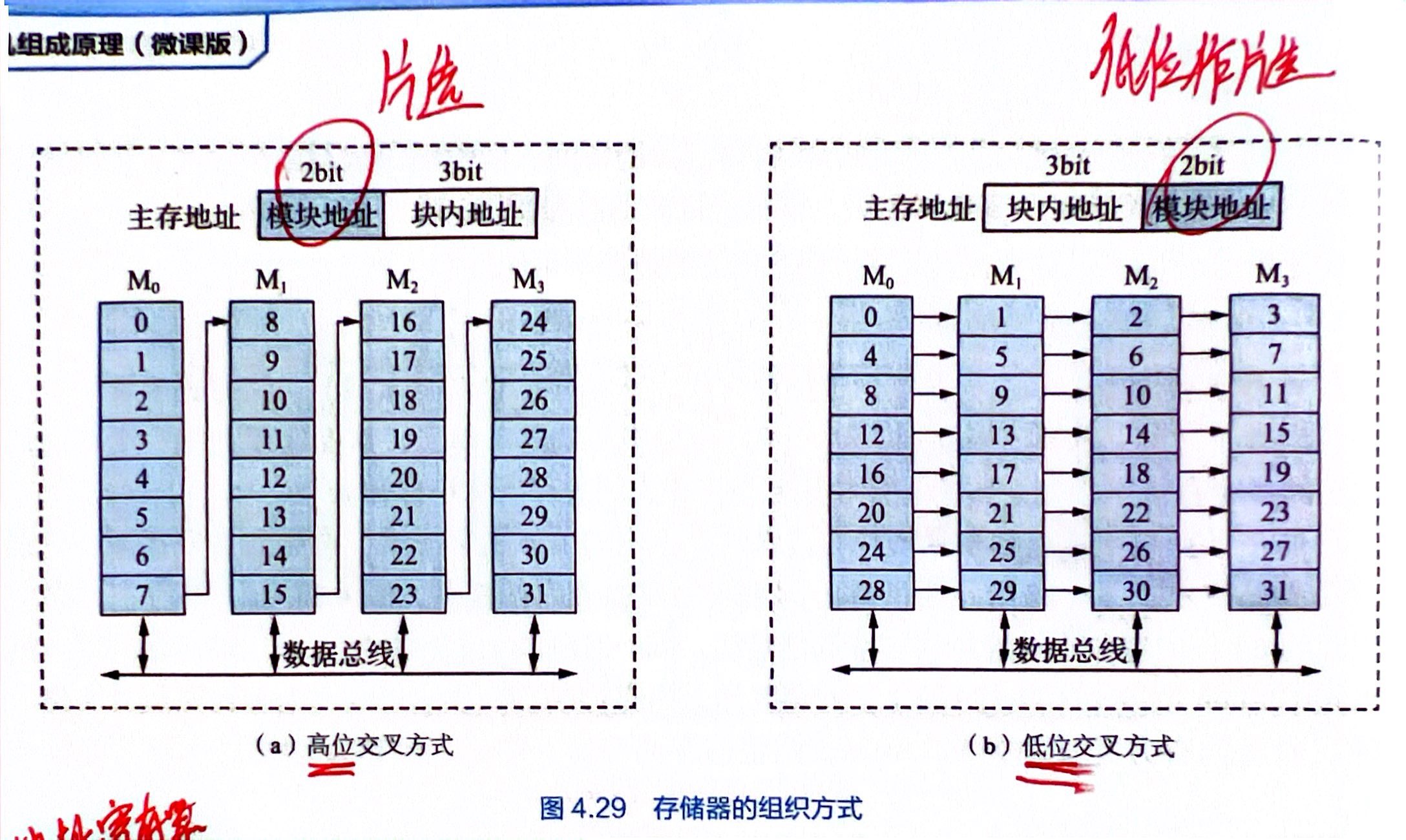

- 高位交叉:

- 相邻地址在同一存储体内

- 不同存储体中的地址不相邻

- 低位交叉:

- 相邻地址在不同存储体内

- 同一存储体中的地址不相邻

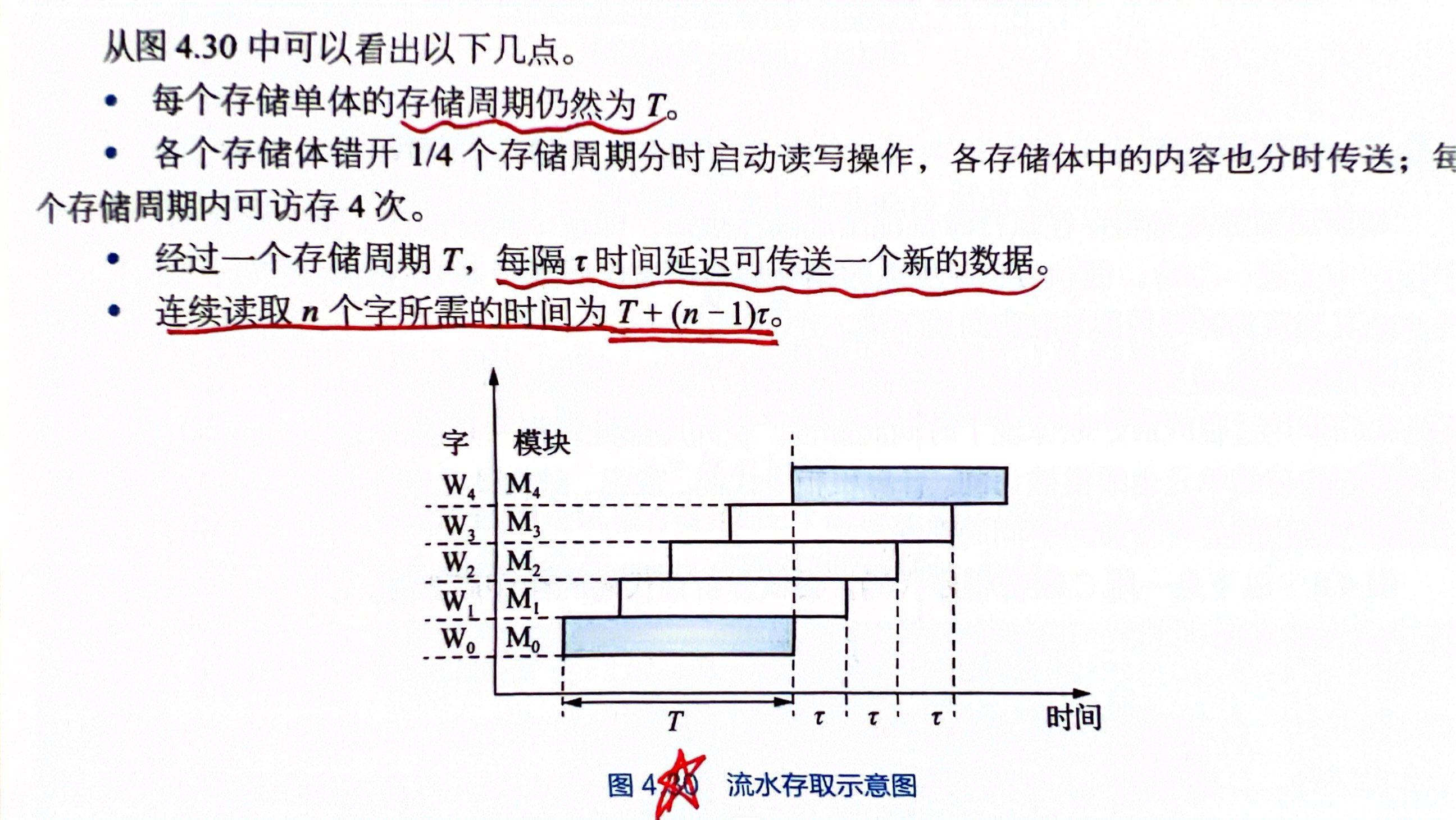

在低位交叉方式下,设存储模块的存储周期为 \(T\),总线传输周期及相应的处理时间延迟总和为 \(\tau\) ,交叉模块数为 \(m=2^k\) ,要实现流水线方式存取,应满足:\(T=m\tau\),连续读取 \(n\) 个字所需时间为 \(T+(n-1)\tau\)

Cache¶

映射方式¶

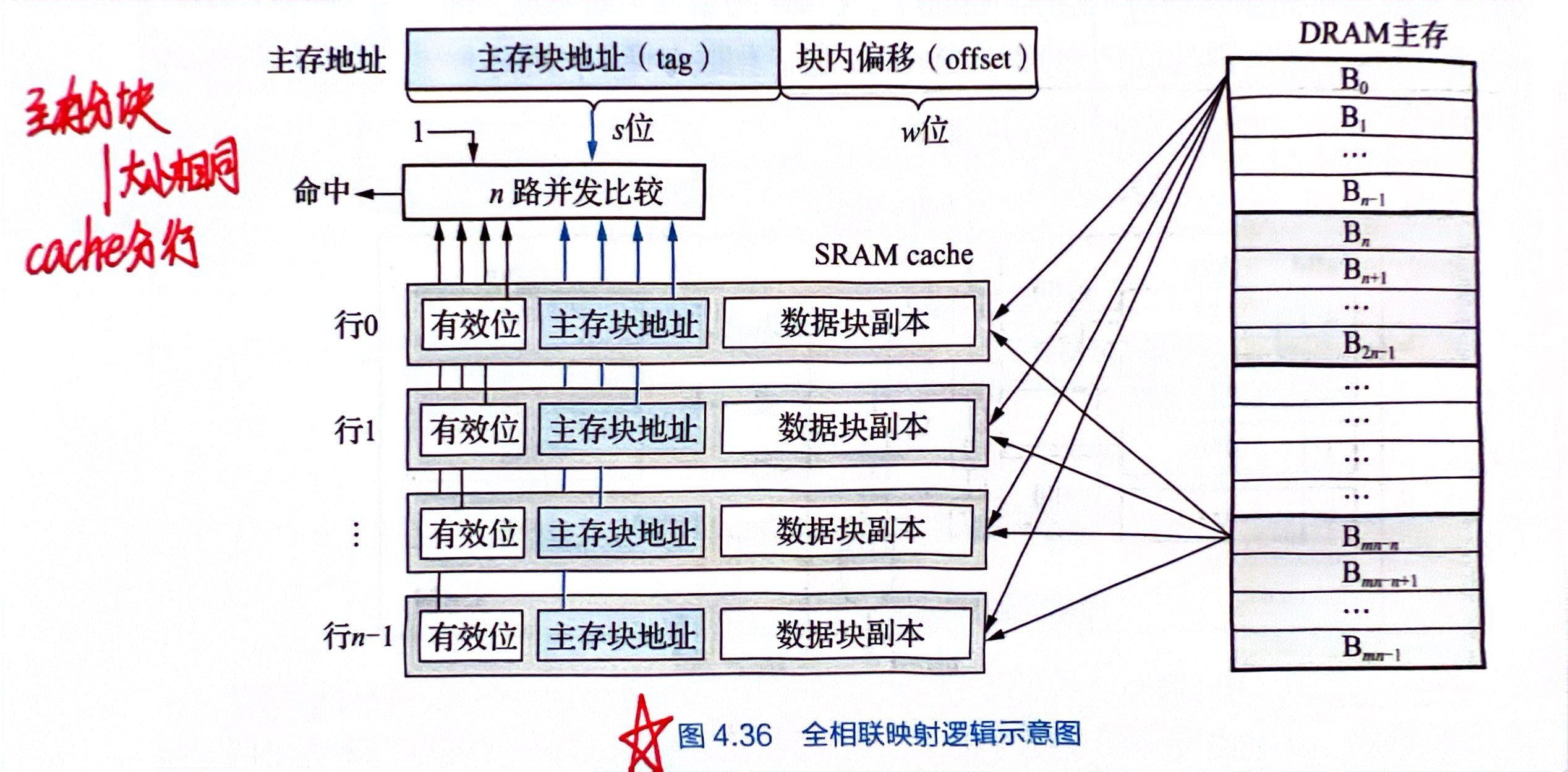

全相联映射:

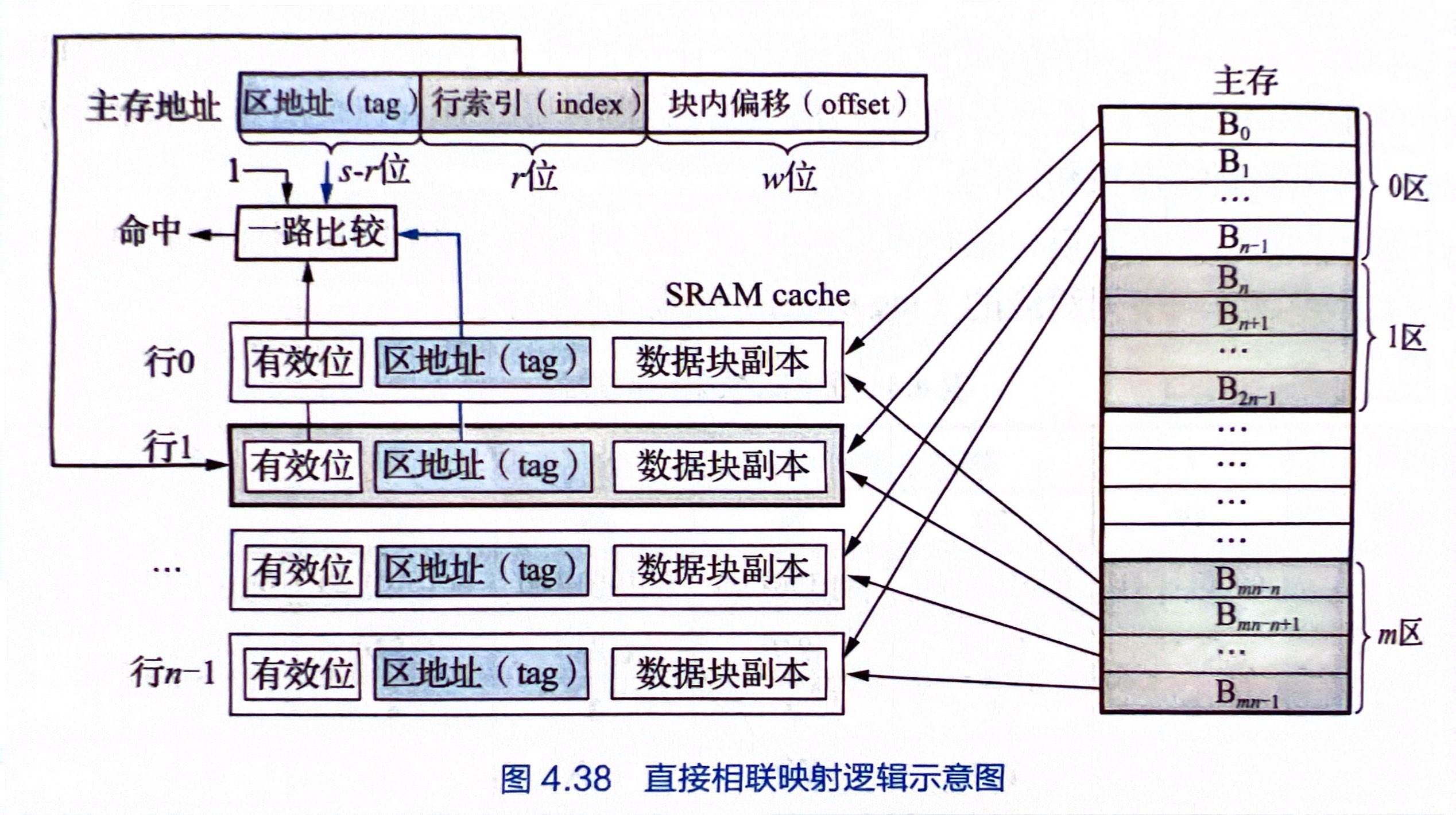

直接相联映射:

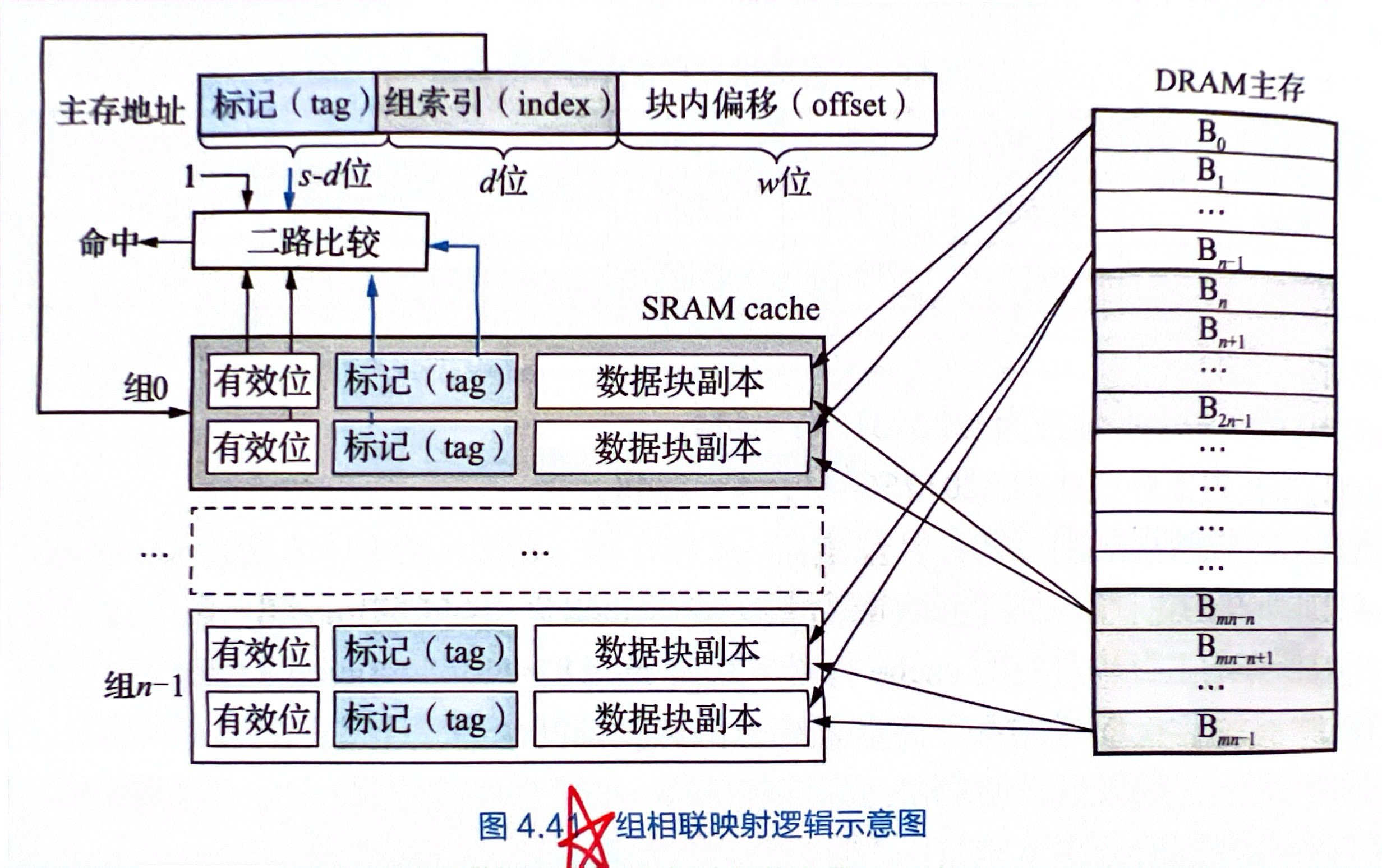

组相联映射:

替换算法¶

- 先进先出算法

- 最不经常使用算法(LFU):被访问行的计数器 +1

- 近期最少使用算法(LRU):被访问行的计数器清零,其余 +1

- 随机替换算法:TLB 采用

写入策略¶

- 写回法(Write-Back, WB):此行被替换时才将脏数据写回主存

- 写穿法(Write-Through, WT):同时对 Cache 和主存进行修改

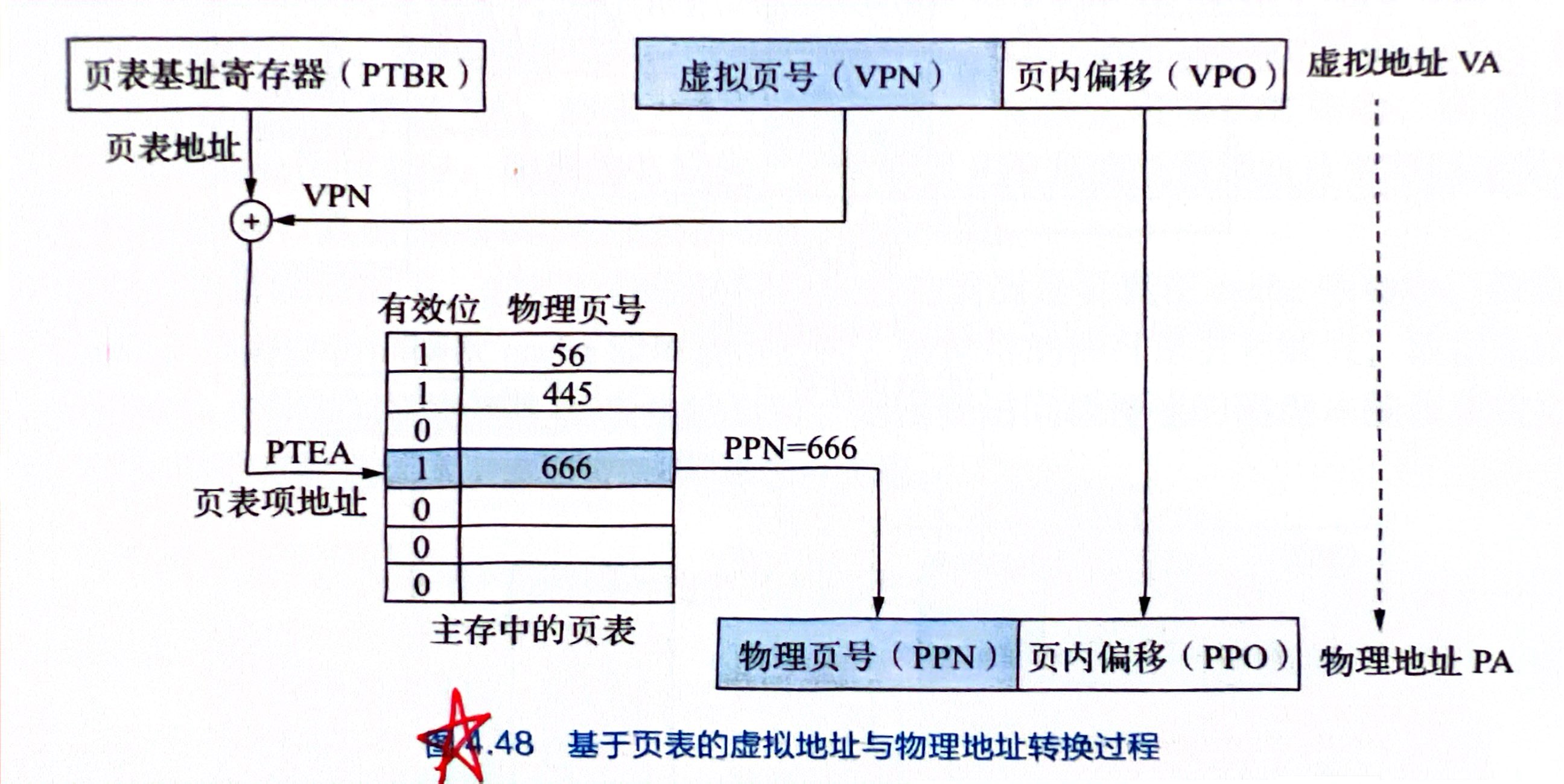

虚拟存储器¶

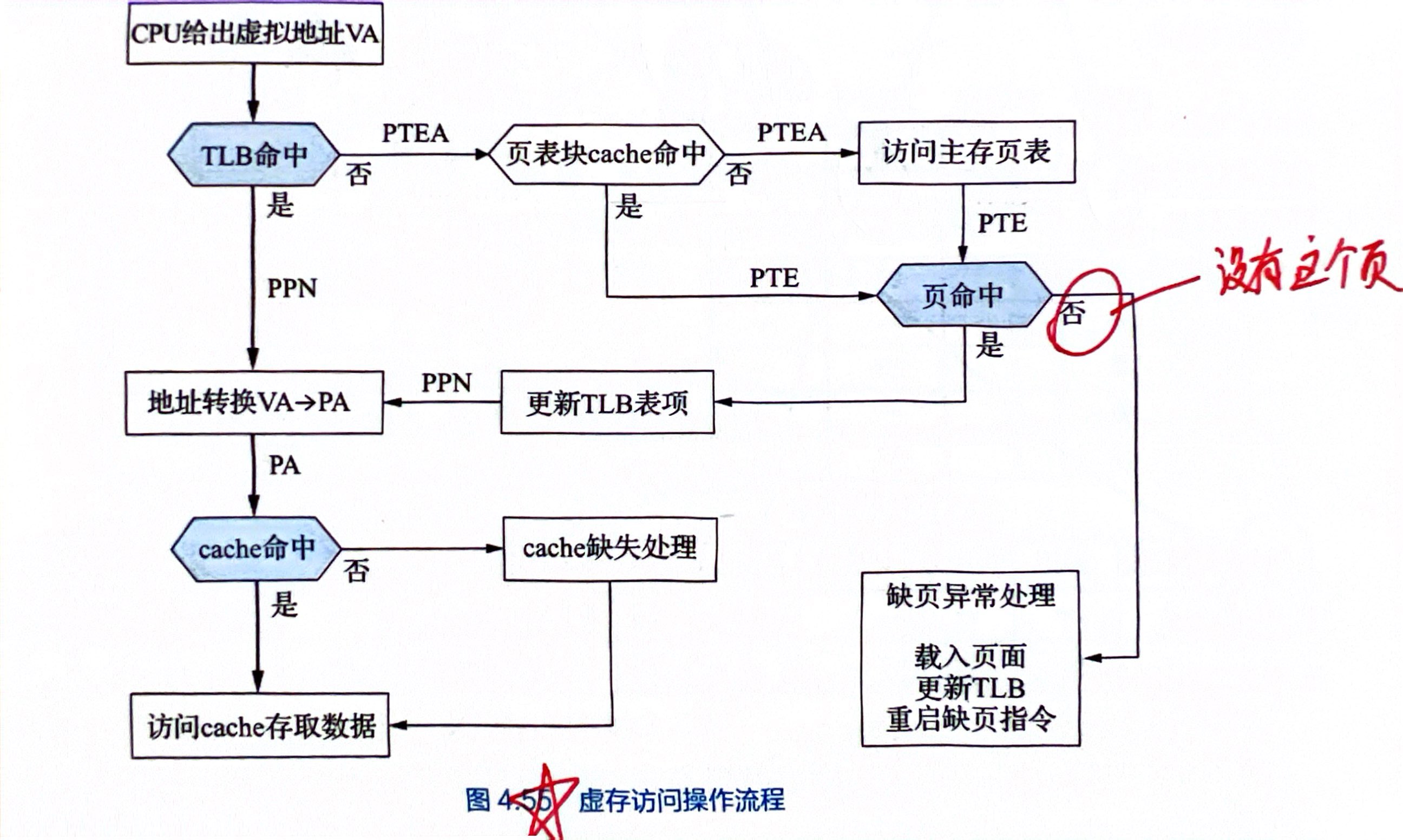

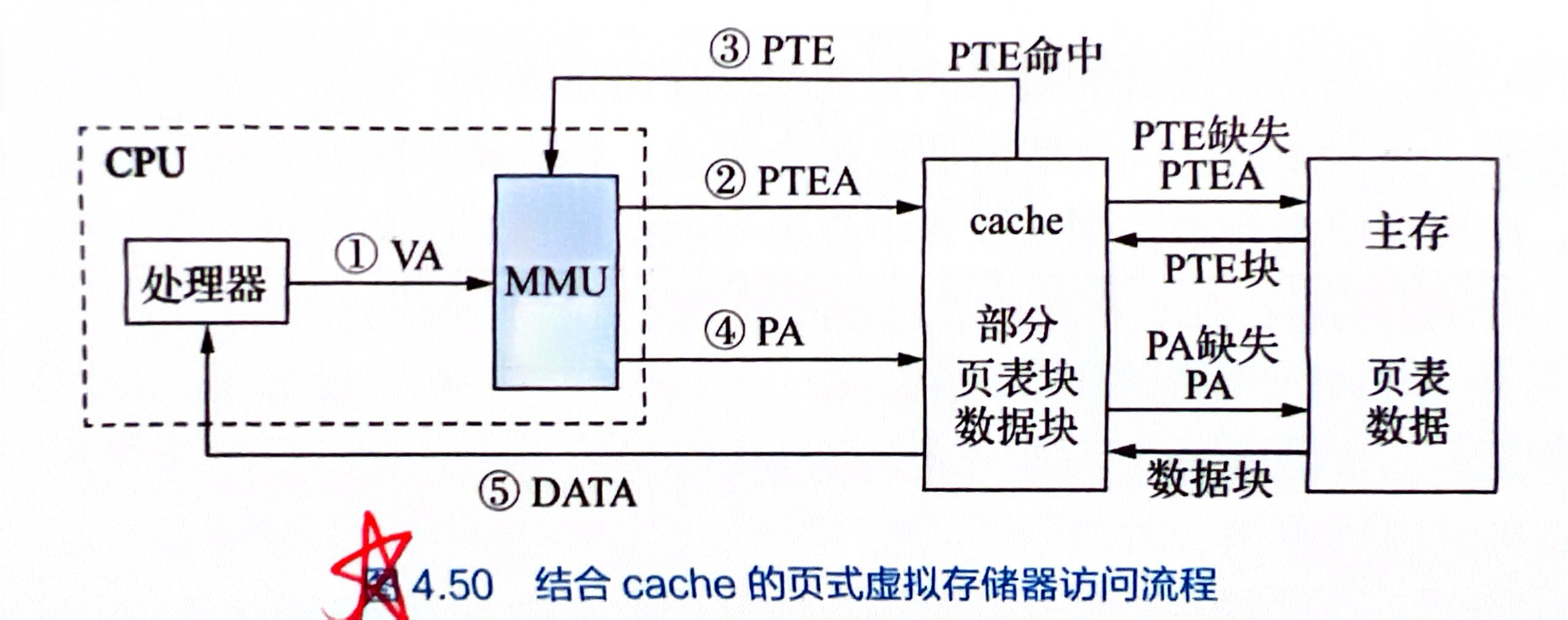

结合 Cache 的虚拟存储器访问流程:

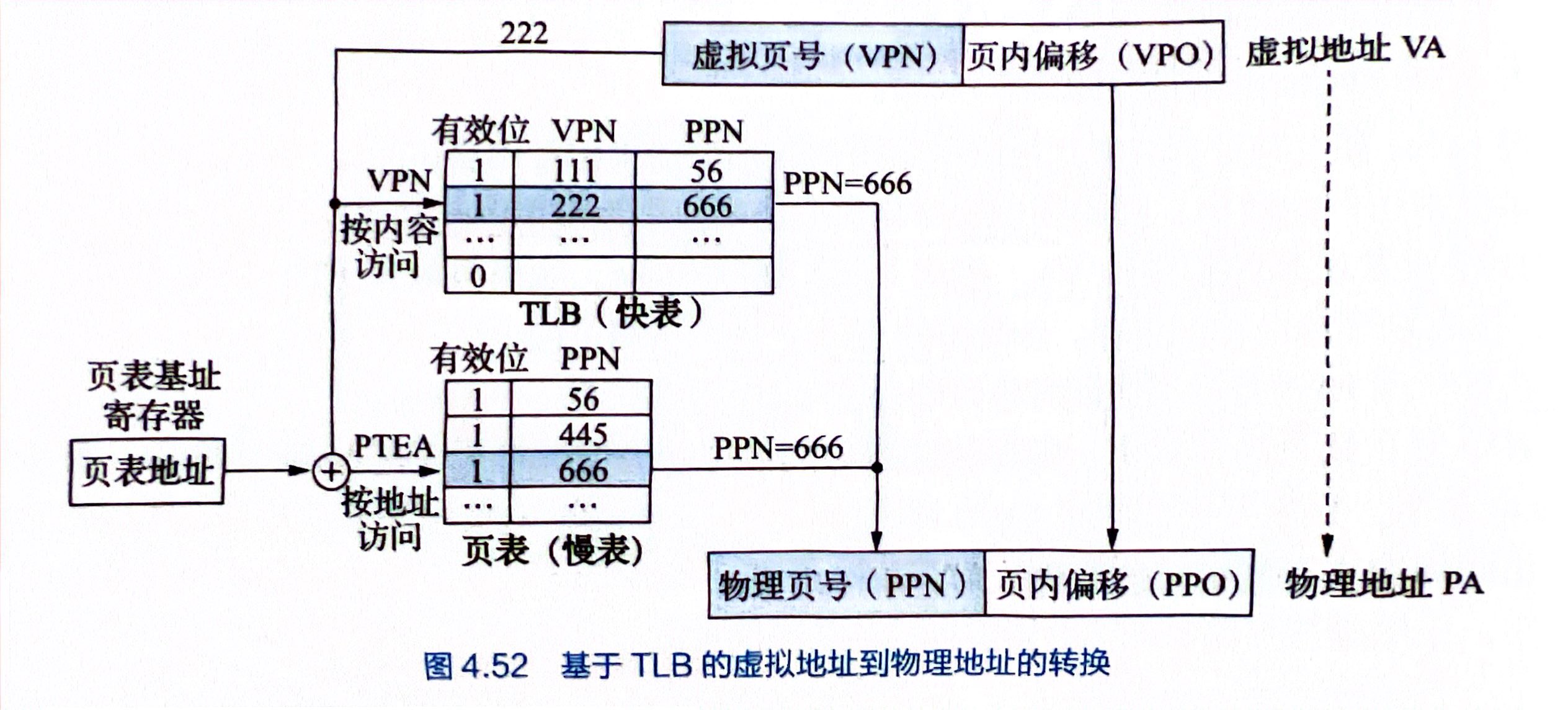

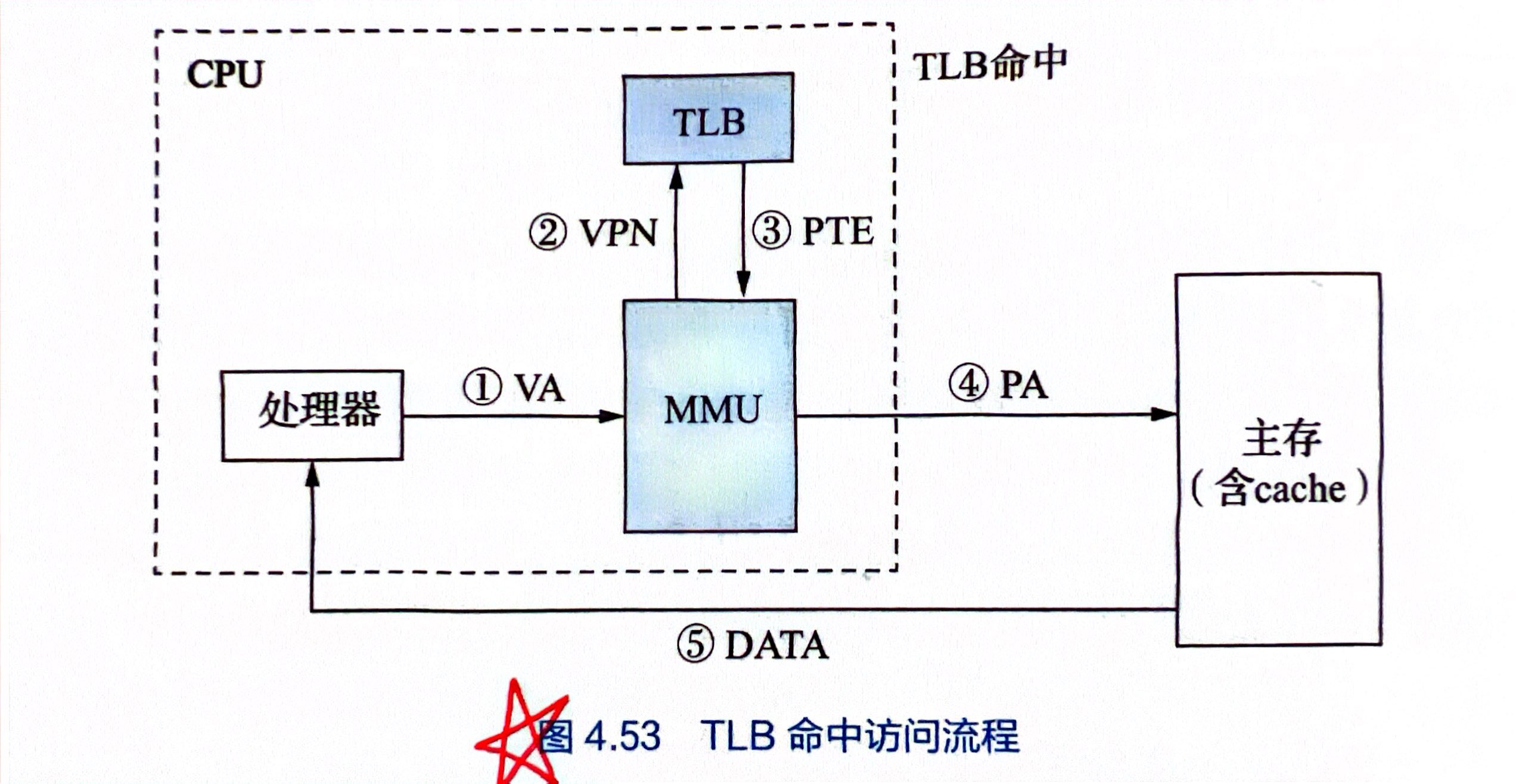

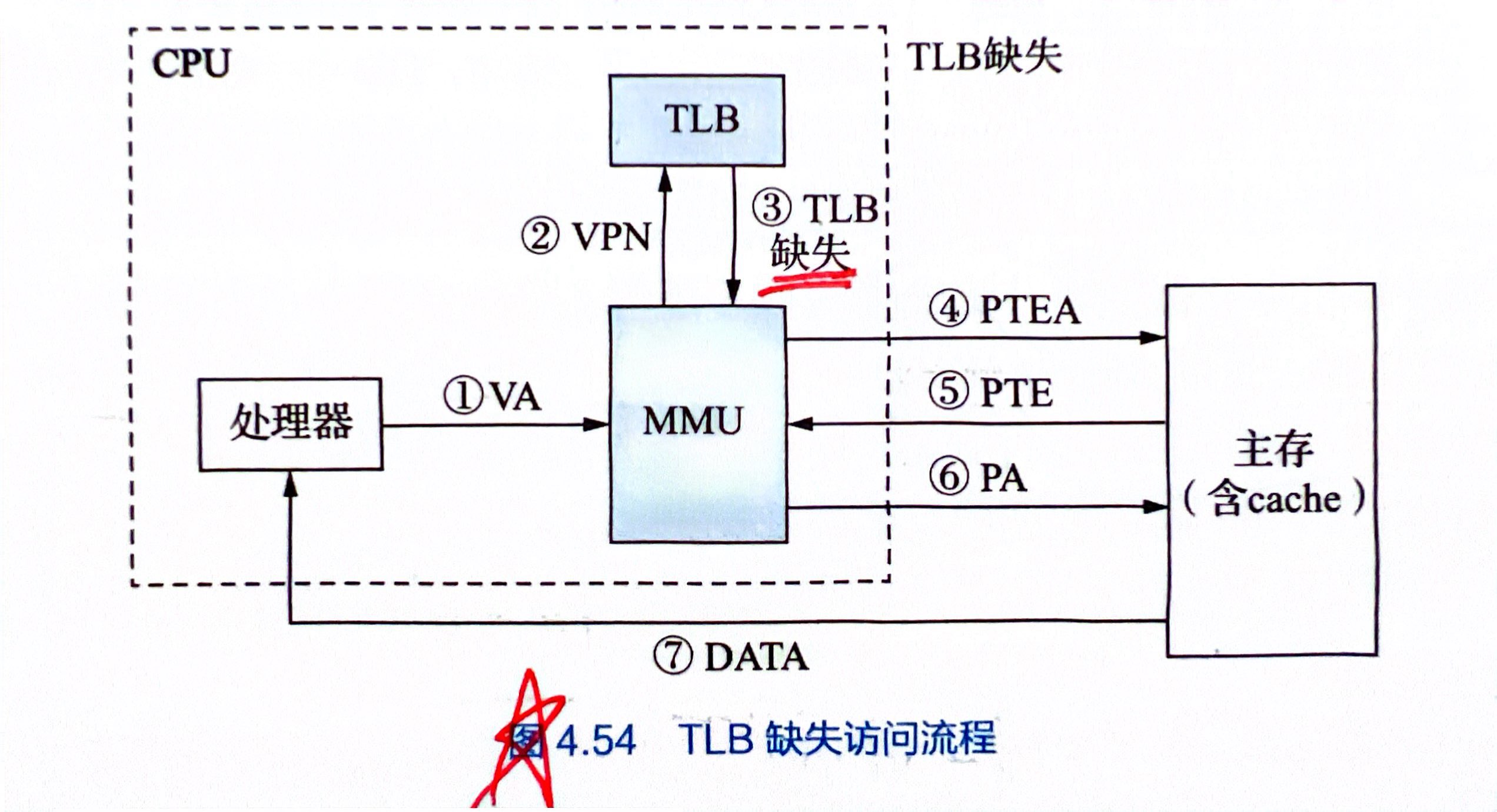

利用 TLB 加速虚拟存储器地址转换:

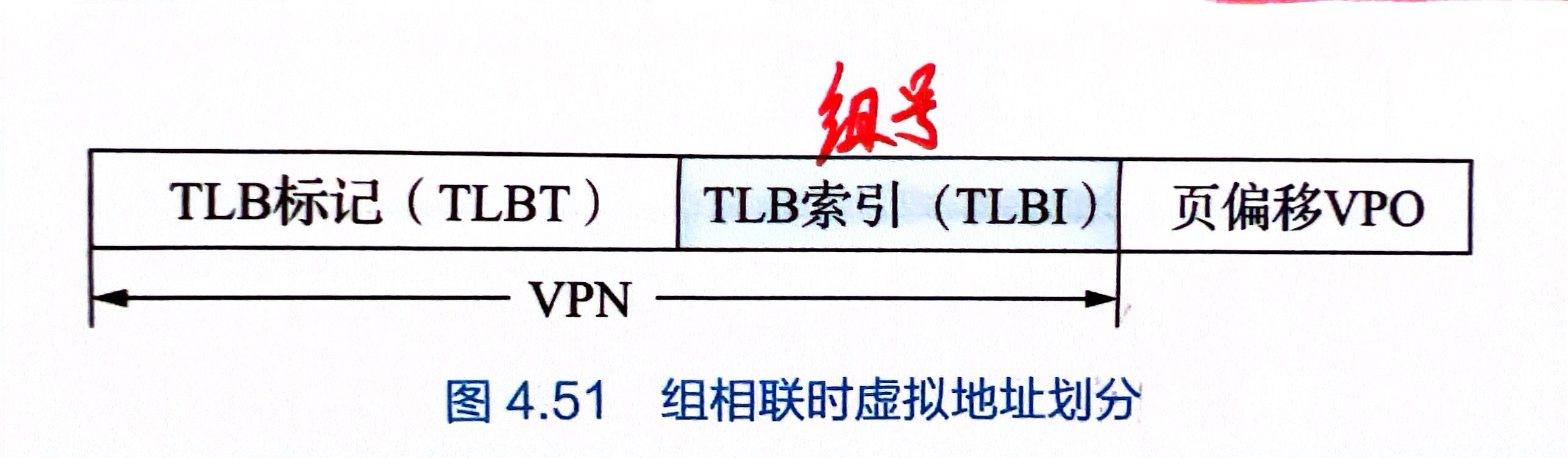

转换旁路缓冲区(TLB):

- 容量较小的 cache

- 大多采用全相联或组相联方式

- 随机替换算法

- TLB 表为快表,主存中的页表为慢表

CPU 访存过程: